Changes are made periodically to the information contained in this manual. These changes will be incorporated into subsequent editions.

Altera Corporation 3525 Monroe Street Santa Clara, CA 95051 (408) 984-2800 TELEX: 888496

Copyright © 1985, 1986, 1987 Altera Corporation. All rights reserved.

No part of this manual may be copied or reproduced in any form or by any means without the prior written permission of Altera Corporation.

A+PLUS, SAM+PLUS, LogicMap, Turbo-Bit, MacroMuncher, SAM, BUSTER, EP310, EP320, EP600, EP610, EP900, EP910, EP1210, EP1800, EPB1400, EPS444, and EPS448 are trademarks of Altera Corporation. LogiCaps is a registered trademark of Altera. WordStar is a registered trademark of MicroPro Corporation. Fido is a trademark of Tom Jennings. MS-DOS is a trademark of Microsoft Corporation. FutureNet DASH is a trademark of FutureNet Corporation. PC-CAPS and PC-LOGS are trademarks of Personal CAD Systems, Inc. IBM Personal Computer is a registered trademark of

International Business Machines Corporation.

# Read This First...

A+PLUS software documentation consists of two manuals:

- A+PLUS User Guide

- A+PLUS Reference Guide

The A+PLUS User Guide provides installation and operation information for the Altera Programmable Logic User System (A+PLUS™). It is divided into three major parts: Introduction to A+PLUS, Design Entry, and Simulation. If you are a first-time user, you are advised to read Sections 1, 2, and 3 in the Introduction to A+PLUS and then—depending on your choice of design entry method—the appropriate section in Design Entry. Some of the design entry packages are optional; therefore, they may not be part of your version of the manual. Each of the design entry sections contains a sample session(s) that guides you through the complete process of programming an EPLD with A+PLUS. Simulation contains the optional Functional Simulator. Following Sections 1 through 3, you will find an Index covering the information in the A+PLUS User Guide, A+PLUS Reference Guide, and the optional packages State Machine Entry and Functional Simulator.

The **A+PLUS Reference Guide** contains detailed information on Altera primitives, the Altera Design File format, APLUS and ADP Menus, Utilization Reports, and A+PLUS messages. Also included are several *Appendixes*, a *Glossary*, and an *Index* covering the information in the **A+PLUS User Guide**, **A+PLUS Reference Guide**, **State Machine Entry**, and *Functional Simulator*.

At the back of each manual, you will find a Customer Comment Form, a Problem Report Card, and a Warranty Card.

A+PLUS hardware and EPLD programming are described in the *LogicMap II* manual.

The A+PLUS User Guide contains the following sections:

#### I. Introduction to A+PLUS

Functional Description Gives an overview of A+PLUS that helps you to determine which design entry method is most appropriate for your particular application, and provides detailed information on the Altera Design Processor.

*Installation* Lists system components and provides specific instructions for installing A+PLUS software.

Getting Started Gives a brief introduction to the menus and menu functions used in running A+PLUS software.

#### II. Design Entry

Boolean Equation Entry Describes how to enter and process a design exclusively with Boolean equations.

State Machine Entry (Option) Describes how to enter and process a design with state machines.

Schematic Capture With FutureNet (Option) Describes how to enter a schematic design with FutureNet's Schematic Designer and process it with A+PLUS.

Altera's schematic capture package, LogiCaps, is described in the *LogiCaps* manual.

#### III. Simulation

Functional Simulator (Option) Explains how to simulate a design with Altera's Functional Simulator.

Index

The A+PLUS Reference Guide contains the following sections:

Altera Primitive Library Describes each Altera primitive in detail, including block diagrams.

Altera Design File Format Explains the format of the Altera Design File.

A+PLUS and ADP Reference Provides detailed descriptions of the APLUS Menu; the user-controllable and automatic functions of the ADP; and DOS command line processing techniques.

*Utilization Report* Explains the Utilization Report and gives sample reports for various Altera EPLDs.

A+PLUS Messages Lists all error, information, and warning messages generated by A+PLUS and the ADP, their causes, and suggestions for corrective action.

Appendix A Part-Specific Information

Appendix B Altera Design File-to-Logic Equation File Translation

Appendix C BNF Rules

Appendix D JEDEC Standard File Format

Appendix E Electronic Design Support Service

Appendix F Altera Primitive Library (Foldouts)

Glossary

Index

# **Manual Updates**

Altera documentation is updated with Change Pages, Section Reprints, and a READ.ME file.

Change Pages are issued for minor changes to the manual. New information is identified with vertical change bars in the margins next to the changed text. In addition, the date of issue is printed at the bottom of each page.

**Section Reprints** are issued if a section requires a substantial number of changes. The date of issue is indicated at the bottom of each page.

A READ.ME File is provided on the A+PLUS INSTALL diskette. This file contains information about recent changes to the A+PLUS software that are not yet reflected in the manual.

# **Printing Conventions**

The following notational conventions are used throughout this manual:

Times Bold - A+PLUS commands, prompts, and

messages

All types of user input

Primitive names

Key names (enclosed in < >'s)

Times Light - Most screen and file output

Helvetica Bold Italics - References to Altera manual titles

Helvetica Light Italics - References to sections within Altera

manuals

Indicates information that requires

special attention

# **Contents**

| Manual Updates<br>Printing Conventions | vii<br>viii |

|----------------------------------------|-------------|

| Section 1: Altera Primitive Library    |             |

| Introduction                           | 1-2         |

| Title Block                            | 1-3         |

| Input Primitives                       | 1-5         |

| INP                                    | 1-6         |

| LINP                                   | 1-7         |

| Logic Primitives                       | 1-8         |

| AND (BNOR)                             | 1-9         |

| BBUF                                   | 1-10        |

| CLKB                                   | 1-11        |

| GND                                    | 1-12        |

| NAND (BOR)                             | 1-13        |

| NOR (BAND)                             | 1-14        |

| NOT                                    | 1-15        |

| OR (BNAND)                             | 1-16        |

| VCC                                    | 1-17        |

|                                        |             |

Read This First

iii

### Section 1: Altera Primitive Library (Continued)

| XNOR                      | 1-18 |

|---------------------------|------|

| XOR                       | 1-19 |

| Equation (EQN) Primitives | 1-20 |

| EQN1                      |      |

| EQN8                      | 1-22 |

| I/O Primitives            | 1-23 |

| COCF                      | 1-24 |

| COIF                      | 1-25 |

| COLF                      | 1-26 |

| CONF                      | 1-27 |

| CORF                      | 1-28 |

| JOJF                      | 1-29 |

| JONF                      | 1-30 |

| NOCF                      | 1-31 |

| NOJF                      | 1-32 |

| NORF                      |      |

| NOSF                      | 1-34 |

| NOTF                      | 1-35 |

| ROCF                      | 1-36 |

| ROIF                      |      |

| ROLF                      |      |

| RONF                      |      |

| RORF                      |      |

| SONF                      |      |

| SOSF                      |      |

| TOIF                      |      |

| TONF                      |      |

| TOTF                      |      |

| Bus I/O Primitives        |      |

| BUSX                      |      |

| LBUSI                     |      |

| LBUSO                     |      |

| LINP8                     |      |

| RBUSI                     |      |

| RINP8                     |      |

|                           |      |

### Section 2: Altera Design File Format

| Functions                                   | 2-2         |

|---------------------------------------------|-------------|

| Syntax                                      | 2-3         |

| Keywords                                    |             |

| White Space and Comments                    | 2-3         |

| Header Section                              | 2-4         |

| Declarations Section                        | 2-6         |

| Network Section                             | 2-8         |

| Equations Section                           | 2-9         |

| End Statement                               | 2-10        |

| Netlist Files                               | 2-13        |

|                                             |             |

| Section 3: A+PLUS and ADP Reference         |             |

| APLUS Menu Functions                        | 2.0         |

| ADP Menu Functions                          | 3-2         |

| Automatic ADP Functions                     |             |

| Running A+PLUS Programs from DOS            | 3-1U        |

| Altera Design Processor                     | ١١-د        |

| Functional Simulator                        | 3-12        |

| FutureNet Pin List Converter                | 3-12        |

| LogiCane                                    | 3-12        |

| Logicaps                                    | 3-13        |

| LogicMap II                                 | 3-14        |

| State Machine Converter                     | 3-14        |

| Section 4: Utilization Report               |             |

| · •                                         | 4.0         |

| Header Information                          | 4-3         |

| Utilization Information                     | 4-4         |

| Outputs, Buried Registers, Inputs, Latches, | and Unused  |

| Resources Subsections                       | 4-4         |

| Part Utilization Subsection                 | 4-5         |

| Macrocell Interconnection Cross Reference   | 4-6         |

| Sample Utilization Reports                  | 4-7         |

| A+PLUS Messages                             |             |

| Error Messages                              | Massages 5  |

| Information Messages                        | Maccanac-20 |

| Warning Massages                            | Massages-29 |

### **Appendixes**

| Appendix A – Part-Specific Information           | A-1    |

|--------------------------------------------------|--------|

| The Altera EPLD Family of Parts                  |        |

| EP310 and EP320                                  | A-3    |

| EP600 and EP610                                  |        |

| EP900 and EP910                                  |        |

| EP1210                                           |        |

| EPB1400 ("BUSTER")                               | A-25   |

| EP1800                                           |        |

| Appendix B – ADF-to-LEF Translation              | R.1    |

| Appendix B = ADI -to-LEI Translation             | ۱ - تا |

| Appendix C – BNF Rules                           | C-1    |

| Appendix D – JEDEC Standard                      |        |

| Design Specification                             | D-1    |

| Note (N) Field                                   |        |

| Programming Information                          |        |

| Bit Count (QF) Field                             |        |

| Security (Ġ) Field                               |        |

| Link (L) Field                                   |        |

| End of Transmission                              |        |

| Legal Characters                                 |        |

| Appendix E – Electronic Design Support Service   | E-1    |

|                                                  |        |

| Appendix F – Altera Primitive Library (Foldouts) | F-1    |

|                                                  |        |

## Glossary

### Index

# Illustrations

| Figure               |                                                                      | Page        |

|----------------------|----------------------------------------------------------------------|-------------|

| 1-1.<br>1-2.         | Altera Title BlockXOR Equivalent Circuit                             | 1-3<br>1-19 |

| 2-1.<br>2-2.         | BNF Syntax for Altera Design FileSample ADF                          |             |

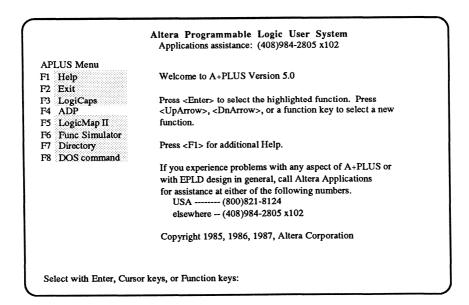

| 3-1.<br>3-2.         | APLUS MenuADP Menu                                                   | 3-2<br>3-6  |

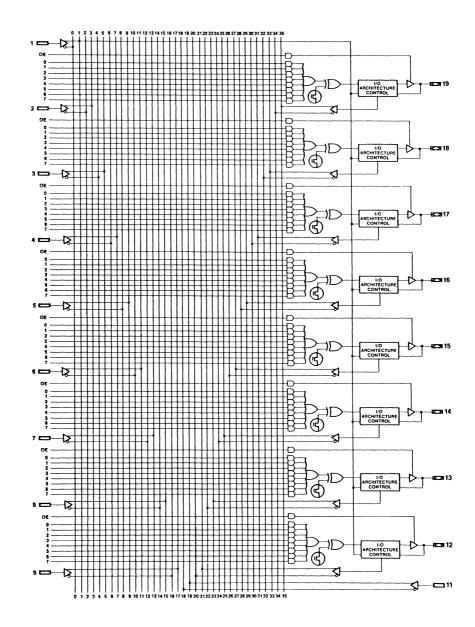

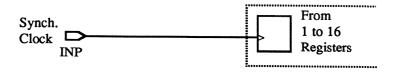

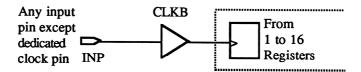

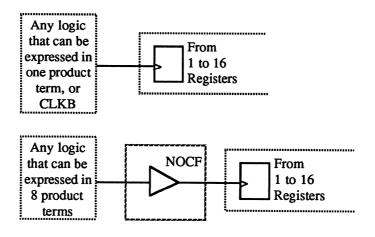

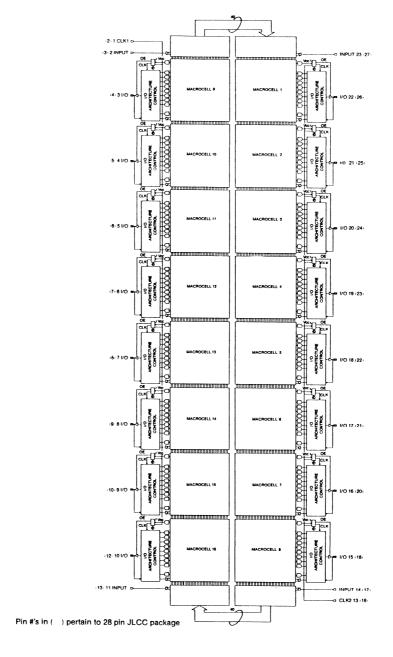

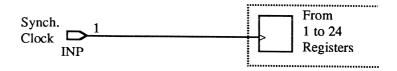

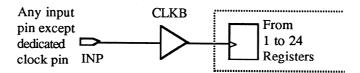

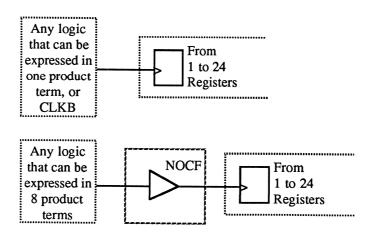

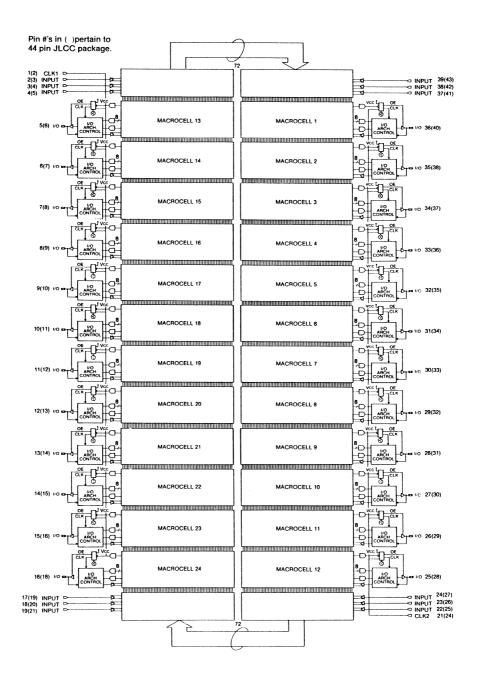

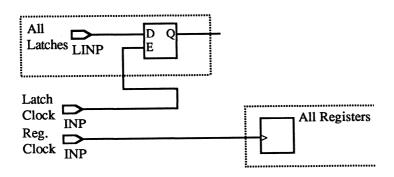

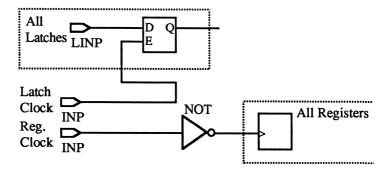

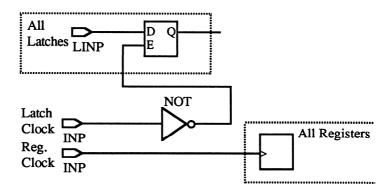

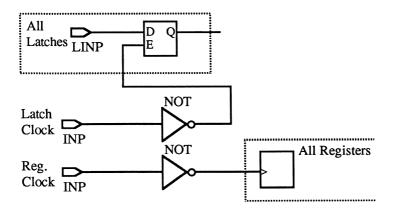

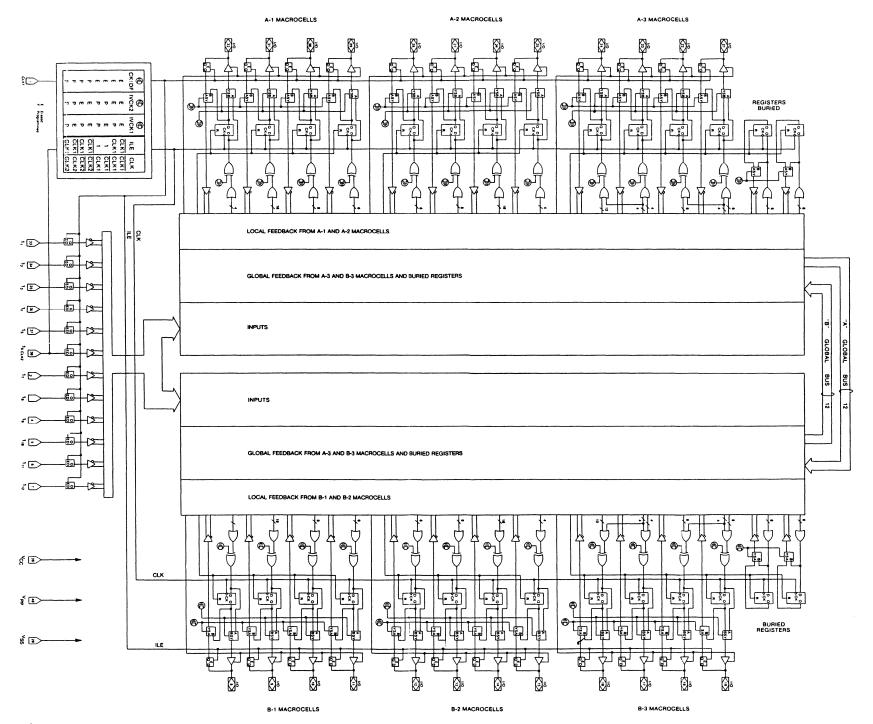

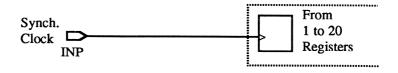

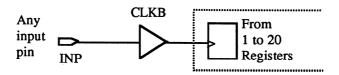

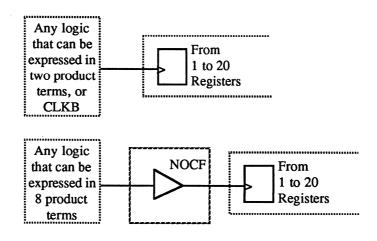

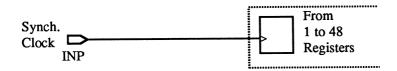

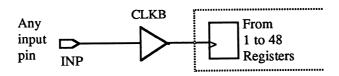

| A-1.<br>A-2.<br>A-3. | EP310/EP320 Clocking<br>EP310 Block Diagram<br>EP320 Block Diagram   | A-6         |

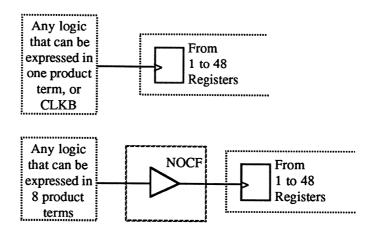

| A-4.<br>A-5.         | EP600/EP610 Clocking<br>EP600/EP610 Block Diagram                    | A-9<br>A-11 |

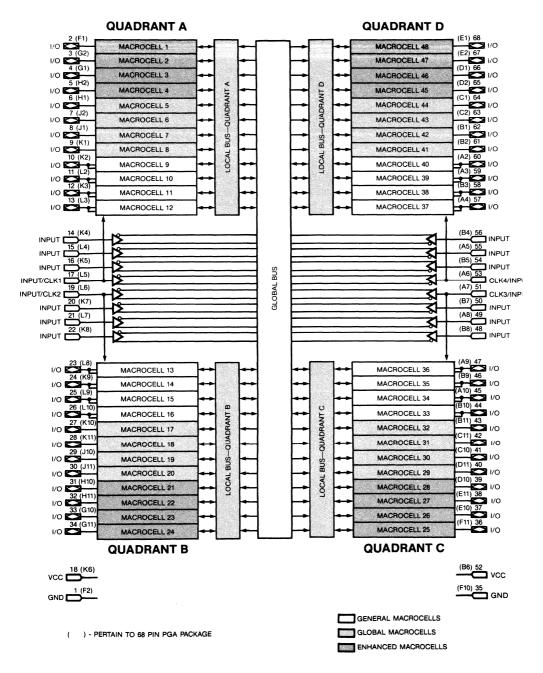

| A-6.<br>A-7.<br>A-8. | EP900/EP910 Clocking<br>EP900/EP910 Block Diagram<br>EP1210 Clocking | A-15        |

| A-9.<br>A-10.        | EP1210 Block DiagramEPB1400 Clocking                                 | A-23        |

| Figure     |                                                          | Page |

|------------|----------------------------------------------------------|------|

|            | EPB1400 Block DiagramEP1800 ClockingEP1800 Block Diagram | A-36 |

| B-1<br>B-2 | Sample Circuit for ADF-to-LEF Translation BEVDIS.LEF     |      |

# **Tables**

| Table                                                |                                                                                                                                                              | Page                                |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 4-1.<br>4-2.<br>4-3.<br>4-4.                         | Sample Utilization Report for EP310<br>Sample Utilization Report for EP600<br>Sample Utilization Report for EPB1400<br>Sample Utilization Report for EP1800J | 4-11<br>4-14                        |

| A-1.<br>A-2.<br>A-3.<br>A-4.<br>A-5.<br>A-6.<br>A-7. | EP310 Macrocell Groups                                                                                                                                       | A-5<br>A-10<br>A-14<br>A-21<br>A-31 |

| B-1.                                                 | ADF-to-LEF Translation                                                                                                                                       | B-2                                 |

| D-1.                                                 | Legal Characters in the JEDEC File                                                                                                                           | D-4                                 |

### SECTION 1

# Altera Primitive Library

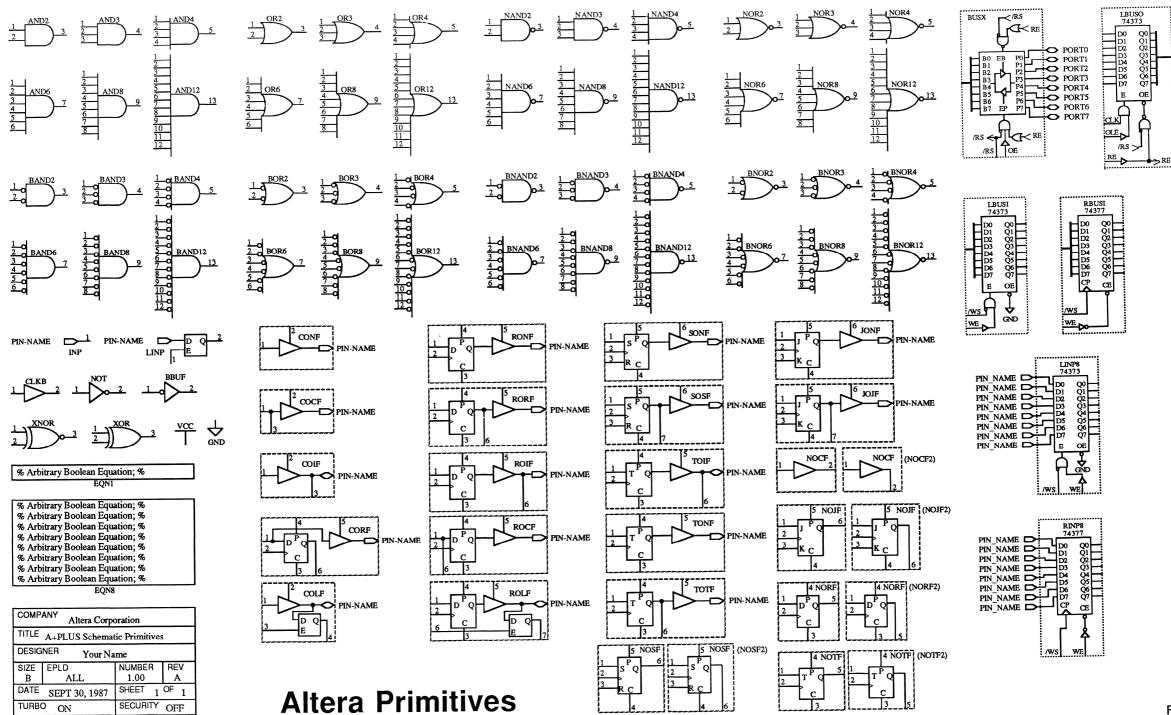

The Altera Primitive Library contains the primitives available for designing circuits in Altera EPLDs. It also includes a title block symbol that provides header information when used with a schematic design entry interface.

This section provides a detailed description of the functions and use of each primitive in the Altera Primitive Library, including schematic diagrams. Primitives are assigned mnemonic names for easy reference. (Refer also to *Appendix F* for foldout pages showing all primitives and a list of which primitives are available for each EPLD.)

For information on the high-level design tools in Altera's Standard and TTL MacroFunction libraries, refer to the manuals for the optional *LogiCaps* and *MacroFunctions* packages.

# Introduction

Altera primitives consist of the following types:

- Input Primitives

- Logic Primitives

- Equation (EQN) Primitives

- I/O Primitives

- Bus I/O Primitives

The following pages list the primitives of each category in alphabetical order. Each primitive description is presented on a separate page and consists of a block diagram that shows pin assignments, followed by detailed information as outlined here:

Name: Gives the name and definition of the primitive. (Logic

primitives have two names: one with the number of inputs appended for the schematic symbol and one for

the Altera Design File.)

ADF Syntax: Shows the appearance of the primitive statement in

the Altera Design File format. (Refer also to Altera

Design File Format).

Description: Defines the input and output signal(s) for the primitive.

EPLDs: Indicates which EPLDs support the primitive.

Note: If necessary, further information is given in notes.

The block diagrams for Altera input, equation, logic and

I/O primitives are shown as they appear on screen when the SN (Symbol Numbers) command is used with the LogiCaps schematic capture package. Some of these primitives may appear in a slightly different form if you are using the FutureNet DASH Schematic

Designer.

## **Title Block**

The Title Block allows you to store information about your circuit design. Each schematic diagram should be documented with an Altera Title Block. Ordinarily, you load and fill out the title block before starting the schematic drawing, then arrange the other symbols within the drawing. The appropriate schematic capture converter module uses the information from the title block to process the schematic. Figure 1-1 shows an Altera Title Block.

For instructions on how to enter the title block into a schematic design, see the individual sections on schematic design entry in the **A+PLUS User Guide**.

| COMPANY Altera Corporation        |                 |      |   |  |  |

|-----------------------------------|-----------------|------|---|--|--|

| TITLE A+PLUS Schematic Primitives |                 |      |   |  |  |

| DESIGNER Your Name                |                 |      |   |  |  |

| SIZE                              | EPLD NUMBER REV |      |   |  |  |

| В                                 | ALL             | 1.00 | Α |  |  |

| DATE SEPT 30, 1987 SHEET 1 OF 1   |                 |      |   |  |  |

| TURBO ON SECURITY OFF             |                 |      |   |  |  |

Figure 1-1. Altera Title Block

The data fields in the title block are as follows:

COMPANY: Company name

TITLE: Title of the drawing

DESIGNER: Your name

SIZE: Drawing size (A, B, C, D, or E)

EPLD: Target device number, i.e., one of the following:

'EP310' | 'EP310D' | 'EP320' | 'EP320D' |

'EP600' | 'EP600D' | 'EP600J' | 'EP610' |

'EP610D' | 'EP610J' | 'EP900' | 'EP900D' |

'EP900J' | 'EP910' | 'EP910D' | 'EP910J' |

'EP1210' | 'EP1210D' | 'EP1210J' | 'EPB1400' |

'EPB1400D' | 'EPB1400J' | 'EP1800' | 'EP1800J'

| 'EP1800G' | 'AUTO' | 'MACRO'

MACRO is used only with the ADLIB option

(available with LogiCaps).

NUMBER: Drawing number

REV: Revision identification

DATE: Date of schematic entry

SHEET: Page identification

TURBO: OFF turns the Turbo-Bit option off (low power). ON

(the default) turns the Turbo-Bit option on (high

speed).

The BUSTER (EPB1400) and EP310 parts do not

support the Turbo-Bit option. LogicMap will ignore any

entry made in this field.

SECURITY: ON turns on the Security Bit, which prevents the

device from being interrogated or inadvertently reprogrammed. OFF turns the Security Bit option off.

# **Input Primitives**

The following pages provide detailed descriptions of the Altera input primitives.

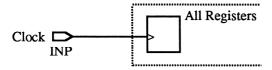

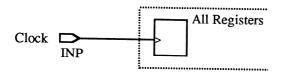

### INP

Name:

INP (Primary Input)

ADF Syntax:

Out = INP(In)

Description:

Outputs:

Out(1) = output to logic array

Inputs:

In = pin input

EPLDs:

ΑII

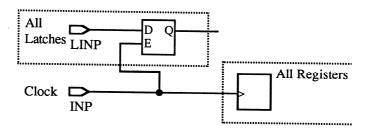

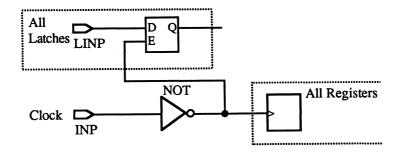

### LINP

Name: LINP (Latched Primary Input)

ADF Syntax: Out = LINP(In,Ile)

Description: Outputs:

Out(2) = latched output to logic array

Inputs:

In = EPLD pin input

Ile(1) = input latch enable (clock input)

EPLDs: EP1210

# **Logic Primitives**

The following pages provide detailed descriptions of the Altera logic primitives. The schematic symbol name for these primitives differs from the Altera Design File primitive name: the symbol name has a suffix indicating the number of inputs (e.g., AND6). Note that for schematic capture entry, the multiple input primitives are available in 2, 3, 4, 6, 8, and 12 input versions.

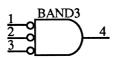

In addition, the AND gates are available as "bubble version" BNOR gates; NAND gates have BOR-gate equivalents; OR gates have BNAND-gate equivalents; and NOR gates have BAND-gate equivalents.

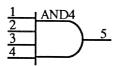

# AND (BNOR)

Schematic Name: AND2, AND3, AND4, AND6, AND8, AND12

ADF Name:

AND(In1, ..., In12)

ADF Syntax:

Out = AND(In1, In2, ..., In12)

Description:

Outputs:

Out = logical AND of inputs

Inputs:

In1, In2, ..., In12 = 2 to 12 inputs

EPLDs:

ΑII

Also available:

BNOR gates ("bubble NOR gates"), which are

AND-gate equivalents. For example:

### **BBUF**

Name: BBUF (Bubble Buffer)

ADF Syntax: Out = BBUF(In1)

Description: Outputs:

Out = inversion of input

Inputs:

In1 = 1 input only

EPLDs: All

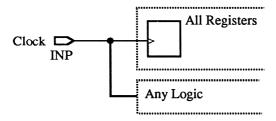

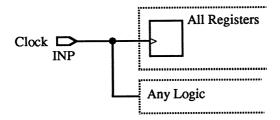

### **CLKB**

Name:

CLKB (Asynchronous Clock Buffer)

ADF Syntax:

Out = CLKB(In)

Description:

Outputs:

Out = output to register clock

Inputs:

In = 1 input only

EPLDs:

EP600, EP610, EP900, EP910, EPB1400.

EP1800

Notes:

- 1. CLKB may be used to request asynchronous clocking of a register when the clock is driven directly from a pin.

- 2. CLKB is optional when the input to a register clock is driven by logic. When CLKBs are fed by logic primitives, the resulting logic must be reducible to one product term, except in the EPB1400 ("BUSTER"), which permits two product terms for the Clock (Clk), Output Latch Enable (Ole), Output Enable (Oe), Read Enable (Re), and Write Enable (We) inputs.

- 3. In the EP600, EP610, EP900, EP910, and EP1800, the asynchronous clock and Output Enable (Oe) inputs share a single product term. When an asynchronous clock is used for the EP600, EP610, EP900, EP910, and the *local* macrocells of the EP1800, Oe must be permanently enabled (VCC). For EP1800 *global* and *all* EPB1400 macrocells, Oe may be set to GND or VCC when asynchronous clocking is used.

### **GND**

Name:

**GND**

ADF Syntax:

**GND**

Description:

The only purpose of this symbol is to assign a node

to ground.

EPLDs:

ΑII

Notes:

1. Node name automatically assigned GND.

2. Does not exist in the P-CAD schematic editor (PC-CAPS). You must use the node name LO or GND. In the P-CAD Simulator (PC-LOGS) you may

use only the name LO.

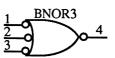

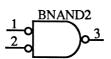

# NAND (BOR)

Schematic Name: NAND2, NAND3, NAND4, NAND6, NAND8,

NAND12

ADF Name: NAND(In1, ..., In12)

ADF Syntax: Out = NAND(In1, In2, ..., In12)

Description: Outputs:

Out = logical NAND of inputs

Inputs:

In1, In2, ..., In12 = 2 to 12 inputs

EPLDs: All

Also available: BOR gates ("bubble OR gates"), which are

NAND-gate equivalents. For example:

$\frac{1}{2} \xrightarrow{BOR3} 4$

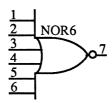

# NOR (BAND)

Schematic Name: NOR2, NOR3, NOR4, NOR6, NOR8, NOR12

ADF Name: NOR(In1, ..., In12)

ADF Syntax: Out = NOR(In1, In2, ..., In12)

Description: Outputs:

Out = logical NOR of inputs

Inputs: In1, In2, ..., In12 = 2 to 12 inputs

EPLDs: All

Also available: BAND gates ("bubble AND gates"), which are

NOR-gate equivalents. For example:

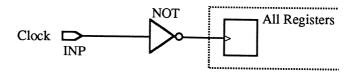

### NOT

Name: NOT (Logical Inversion)

ADF Syntax: Out = NOT(In1)

Description: Outputs:

Out = inversion of input

Inputs: In1 = 1 input only

EPLDs: All

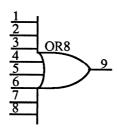

# OR (BNAND)

Schematic Name: OR2, OR3, OR4, OR6, OR8, OR12

ADF Name: OR(In1, ..., In12)

ADF Syntax: Out = OR(In1, In2, ..., In12)

Description: Outputs:

Out = logical OR of inputs

Inputs:

In1, In2, ..., In12 = 2 to 12 inputs

EPLDs: All

Also available: BNAND gates ("bubble NAND gates"), which

are OR-gate equivalents. For example:

### VCC

VCC

Name:

VCC

ADF Syntax:

VCC

Description:

The only purpose of this symbol is to assign a node

to VCC.

EPLDs:

ΑII

Notes:

1. Node name automatically assigned VCC.

2. Does not exist in the P-CAD schematic editor (PC-CAPS). You must name the node VCC or HI. (In the P-CAD Simulator [PC-LOGS] you may use

only the name HI.)

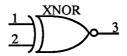

### **XNOR**

Name:

XNOR (Logical Exclusive NOR)

ADF Syntax:

Out = XNOR(In1, In2)

Description:

Outputs:

Out = exclusive NOR of inputs

Inputs:

In1, In2 = 2 inputs only

EPLDs:

ΑII

Note:

Converted into equivalent logic function using two

NOT, two AND, and one NOR primitive by the

Translator.

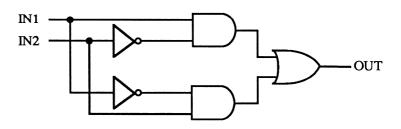

### XOR

Name: XOR (Logical Exclusive OR)

ADF Syntax: Out = XOR(In1, In2)

Description: Outputs:

Out = exclusive OR of inputs

Inputs:

In1, In2 = 2 inputs only

EPLDs: All

Note: Converted by the Translator into an equivalent logic

function using two NOT, two AND, and one OR

primitive. See Figure 1-2.

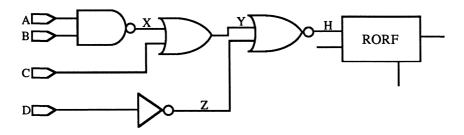

Figure 1-2. XOR Equivalent Circuit

# **Equation (EQN) Primitives**

The following pages provide detailed descriptions of the Altera equation primitives, which are used for entering Boolean equations with schematic capture programs. These two primitives, labeled EQN1 and EQN8, can accommodate one and eight arbitrary Boolean expressions, respectively. (Refer to the documentation for individual schematic capture programs for how to create EQN primitives with any number of equations.)

# EQN<sub>1</sub>

% Arbitrary Boolean Equation; %

EQN1

Schematic Name: EQN1

ADF Name: EQN

ADF Syntax: Out = arbitrary Boolean expression;

(must be terminated with a semicolon)

Description: This equation box is intended to accommodate

one arbitrary Boolean expression.

EPLDs: All

#### EQN8

% Arbitrary Boolean Equation; %

EQN8

Schematic Name: EQN8

ADF Name: EQN

ADF Syntax: Out = arbitrary Boolean expression;

(must be terminated with a semicolon)

Description: This equation box is intended to accommodate

eight arbitrary Boolean expressions.

EPLDs: All

# I/O Primitives

The following pages provide detailed descriptions of the Altera I/O primitives.

The following rules apply to I/O primitives:

- 1. If the Output Enable (Oe) is unconnected, it defaults to VCC (output enabled).

- 2. The default for an unconnected Clear (C) is GND (clear disabled).

- 3. The default for an unconnected Preset (P) is GND (preset disabled).

- 4. The Clock (Clk) must be assigned under all circumstances.

- 5. The letters that comprise the mnemonic names of I/O primitives have the following meanings:

C = Combinatorial

F = Feedback

I = I/O

J = JK-type flipflop

L = Latched

N = No

O = Output

R = (Registered) D-type flipflop

S = SR-type flipflop

T = T-type flipflop

# COCF

Name:

COCF (Combinatorial Output, Combinatorial

Feedback)

ADF Syntax:

Out,Fbk = COCF(In,Oe)

Description:

Outputs:

Out Fbk(3) output to EPLD pinfeedback to logic array

Inputs:

In(1) = input from logic array

Oe(2) = 3-state buffer output enable input

EPLDs:

EP310, EPB1400, EP1800

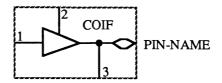

# COIF

Name: COIF (Combinatorial Output, I/O Feedback)

ADF Syntax: Out,Fbk = COIF(In,Oe)

Description: Outputs:

Out = output to EPLD pin Fbk(3) = feedback to logic array

Inputs:

In(1) = input from logic array

Oe(2) = 3-state buffer output enable input

EPLDs: All

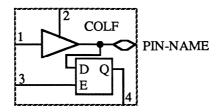

#### COLF

Name: COLF (Combinatorial Output, Latched Feedback)

ADF Syntax: Out,Fbk = COLF(In,Oe,Ile)

Description: Outputs:

Out = output to EPLD pin Fbk(4) = feedback to logic array

Inputs:

In(1) = input from logic array

Oe(2) = 3-state buffer output enable input

Ile(3) = latch clock input

EPLDs: EP1210

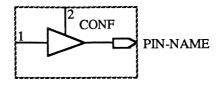

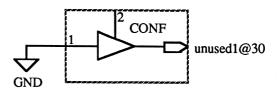

# CONF

Name: CONF (Combinatorial Output, No Feedback)

ADF Syntax: Out = CONF(In,Oe)

Description: Outputs:

Out = output to EPLD pin

Inputs:

In(1) = input from logic array

Oe(2) = 3-state buffer output enable input

EPLDs: All

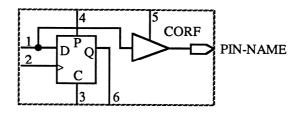

#### CORF

Name:

CORF (Combinatorial Output, Registered

Feedback)

ADF Syntax:

Out,Fbk = CORF(In,Clk,C,P,Oe)

Description:

Outputs:

Out = output to EPLD pin Fbk(6) = feedback to logic array

Inputs:

In(1) = input from logic array Clk(2) = register clock input

C(3) = clear input

P(4) = preset input (not used in

EP1210)

Oe(5) = 3-state buffer output enable

input

EPLDs:

EP310, EP1210

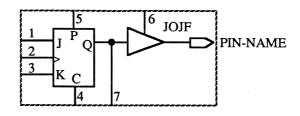

# **JOJF**

Name: JOJF (JK Output, JK Feedback)

ADF Syntax: Out,Fbk = JOJF(JIn,Clk,KIn,C,P,Oe)

Description: Outputs:

Out = output to EPLD pin Fbk(7) = feedback to logic array

Inputs:

JIn(1) = input from logic array

Clk(2) = register clock

KIn(3) = input from logic array

C(4) = clear input

P(5) = preset input (not used in

EP600, EP610, EP900, EP910, EPB1400, EP1800)

Oe(6) = 3-state buffer output enable

input

EPLDs: EP600, EP610, EP900, EP910, EPB1400,

## **JONF**

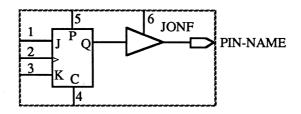

Name: JONF (JK Output, NO Feedback)

ADF Syntax: Out = JONF(JIn,Clk,KIn,C,P,Oe)

Description: Outputs:

Out = output to EPLD pin

Inputs:

JIn(1) = input from logic array Clk(2) = register clock input KIn(3) = input from logic array

C(4) = clear input

P(5) = preset input (not used in EP600, EP610, EP900,

EP910, EPB1400, EP1800)

Oe(6) = 3-state buffer output enable

input

EPLDs: EP600, EP610, EP900, EP910, EPB1400,

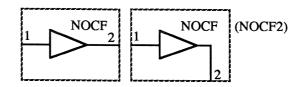

## NOCF

Name: NOCF (No Output, Combinatorial Feedback)

ADF Syntax: Fbk = NOCF(In)

Description: Outputs:

Fbk(2) = feedback to logic array

Inputs:

In(1) = input from logic array

EPLDs: EP310, EP1210, EPB1400, EP1800

Note: 1. In the EP1210, NOCF can only be used on the

four macrocells without I/O pins (buried macrocells). If combinatorial feedback is needed on a macrocell with an I/O pin, the NOCF is promoted to a COIF

primitive.

2. If used in the EP320, EP600, EP610, EP900, or

EP910, the NOCF is promoted to a COIF.

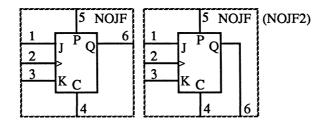

#### NOJF

Name: NOJF (No Output, JK Feedback)

ADF Syntax: Fbk = NOJF(JIn,Clk,KIn,C,P)

Description: Outputs:

Fbk(6) = feedback to logic array

Inputs:

JIn(1) = input from logic array Clk(2) = register clock input KIn(3) = input from logic array

C(4) = clear input

P(5) = preset input (not used in

EP600, EP610, EP900,

EP910, EPB1400, EP1800)

EPLDs: EP600, EP610, EP900, EP910, EPB1400,

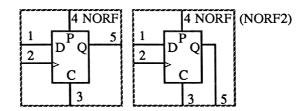

#### NORF

Name: NORF (No Output, Registered Feedback)

ADF Syntax: Fbk = NORF(In,Clk,C,P)

Description: Outputs:

Fbk(5) = feedback to logic array

Inputs:

In(1) = input from logic array Clk(2) = register clock input

C(3) = clear input

P(4) = preset input (not used in

EP600, EP610, EP900, EP910, EP1210, EPB1400,

EP1800)

EPLDs: All

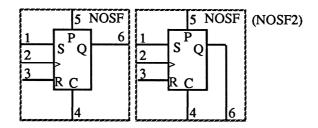

## NOSF

Name:

NOSF (No Output, SR Feedback)

ADF Syntax:

Fbk = NOSF(SIn,Clk,RIn,C,P)

Description:

Outputs:

Fbk(6) = feedback to logic array

Inputs:

SIn(1) = input from logic array Clk(2) = register clock input RIn(3) = input from logic array

C(4) = clear input

P(5) = preset input (not used in

EP600, EP610, EP900,

EP910, EPB1400, EP1800)

EPLDs:

EP600, EP610, EP900, EP910, EPB1400,

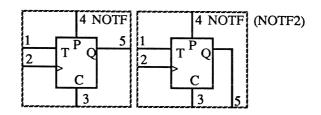

# **NOTF**

Name:

NOTF (No Output, T Feedback)

ADF Syntax:

Fbk = NOTF(In,Clk,C,P)

Description:

Outputs:

Fbk(6) = feedback to logic array

Inputs:

In(1) = input from logic array Clk(2) = register clock input

C(4) = clear input

P(5) = preset input (not used in

EP600, EP610, EP900, EP910, EPB1400, EP1800)

EPLDs:

EP600, EP610, EP900, EP910, EPB1400,

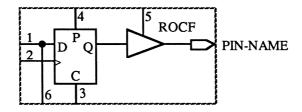

#### ROCF

Name: ROCF (Registered Q Output, Combinatorial

Feedback)

ADF Syntax: Out, Fbk = ROCF(In, Clk, C, P, Oe)

Description: Outputs:

Out = output to EPLD pin Fbk(6) = feedback to logic array

Inputs:

In(1) = input from logic array

C1k(2) = register clock C(3) = clear input P(4) = preset input

Oe(5) = 3-state buffer output enable

input

EPLDs: EP310

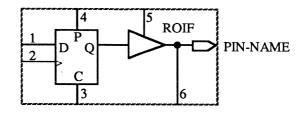

#### ROIF

Name:

ROIF (Registered Q Output, I/O Feedback)

ADF Syntax:

Out,Fbk = ROIF(In,Clk,C,P,Oe)

Description:

Outputs:

Out = output to EPLD pin Fbk(6) = feedback to logic array

Inputs:

In(1) = input from logic array

Clk(2) = register clock C(3) = clear input

P(4) = preset input (not used in

EP600, EP610, EP900, EP910, EP1210, EPB1400,

EP1800)

Oe(5) = 3-state buffer output enable

input

EPLDs:

EP310, EP600, EP610, EP900, EP910, EP1210,

EPB1400, EP1800

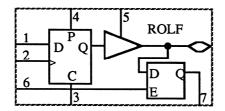

## ROLF

Name: ROLF (Registered Q Output, Latched Feedback)

ADF Syntax: Out,Fbk = ROLF(In,Clk,C,P,Oe,Ile)

Description: Outputs:

Out = output to EPLD pin Fbk(7) = feedback to logic array

Inputs:

In(1) = input from logic array Clk(2) = register clock input

C(3) = clear input

P(4) = preset input (not used in

EP1210)

Oe(5) = 3-state buffer output enable

input

Ile(6) = latch clock input

EPLDs: EP1210

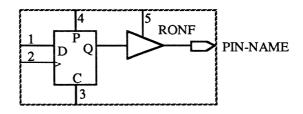

# RONF

Name: RONF (Registered Q Output, No Feedback)

ADF Syntax: Out = RONF(In,Clk,C,P,Oe)

Description: Outputs:

Out = output to EPLD pin

Inputs:

In(1) = input from logic array Clk(2) = register clock input

C(3) = clear input

P(4) = preset input (not used in

EP320, EP600, EP610, EP900, EP910, EP1210, EPB1400, EP1800)

Oe(5) = 3-state buffer output enable

input

EPLDs: All

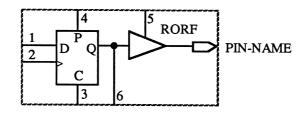

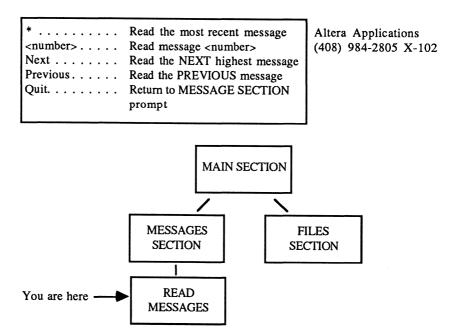

#### RORF

Name:

RORF (Registered Q Output, Registered

Feedback)

ADF Syntax:

Out,Fbk = RORF(In,Clk,C,P,Oe)

Description:

Outputs:

Out = output to EPLD pin Fbk(6) = feedback to logic array

Inputs:

In(1) = input from logic array Clk(2) = register clock input

C(3) = clear input

P(4) = preset input (not used in

EP320, EP600, EP610, EP900, EP910, EP1210,

EPB1400, EP1800)

Oe(5) = 3-state buffer output enable

input

EPLDs:

All

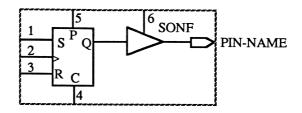

## SONF

Name: SONF (SR Output, No Feedback)

ADF Syntax: Out = SONF(SIn,Clk,RIn,C,P,Oe)

Description: Outputs:

Out = output to EPLD pin

Inputs:

SIn(1) = input from logic array Clk(2) = register clock input RIn(3) = input from logic array

C(4) = clear input

P(5) = preset input (not used in

EP600, EP610, EP900, EP910, EPB1400, EP1800)

Oe(6) = 3-state buffer output enable

input

EPLDs: EP600, EP610, EP900, EP910, EPB1400,

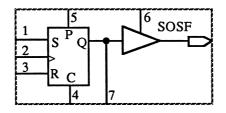

# SOSF

Name:

SOSF (SR Output, SR Feedback)

ADF Syntax:

Out,Fbk = SOSF(SIn,Clk,RIn,C,P,Oe)

Description:

Outputs:

Out = output to EPLD pin Fbk(7) = feedback to logic array

Inputs:

SIn(1) = input from logic array Clk(2) = register clock input RIn(3) = input from logic array

C(4) = clear input

P(5) = preset input (not used in

EP600, EP610, EP900, EP910, EPB1400, EP1800)

Oe(6) = 3-state buffer output enable

input

EPLDs:

EP600, EP610, EP900, EP910, EPB1400,

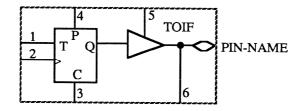

# TOIF

Name: TOIF (T Output, I/O Feedback)

ADF Syntax: Out, Fbk = TOIF(In, Clk, C, P, Oe)

Description: Outputs:

Out = output to EPLD pin Fbk(6) = feedback to logic array

Inputs:

In(1) = input from logic array Clk(2) = register clock input

C(3) = clear input

P(4) = preset input (not used in

EP600, EP610, EP900, EP910, EPB1400, EP1800)

Oe(5) = 3-state buffer output enable

input

EPLDs: EP600, EP610, EP900, EP910, EPB1400,

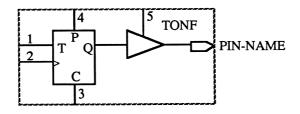

#### TONE

Name:

TONF (T Output, No Feedback)

ADF Syntax:

Out = TONF(In,Clk,C,P,Oe)

Description:

Outputs:

Out = output to EPLD pin

Inputs:

In(1) = input from logic array Clk(2) = register clock input

C(3) = clear input

P(4) = preset input (not used in

EP600, EP610, EP900,

EP910, EPB1400, EP1800)

Oe(5) = 3-state buffer output enable

input

EPLDs:

EP600, EP610, EP900, EP910, EPB1400,

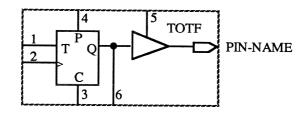

# **TOTF**

Name:

TOTF (T Output, T Feedback)

ADF Syntax:

Out,Fbk = TOTF(In,Clk,C,P,Oe)

Description:

Outputs:

Out = output to EPLD pin Fbk(6) = feedback to logic array

Inputs:

In(1) = input from logic array Clk(2) = register clock input

C(3) = clear input

P(4) = preset input (not used in

EP600, EP610, EP900, EP910, EPB1400, EP1800)

Oe(5) = 3-state buffer output enable

input

EPLDs:

EP600, EP610, EP900, EP910, EPB1400,

# **Bus I/O Primitives**

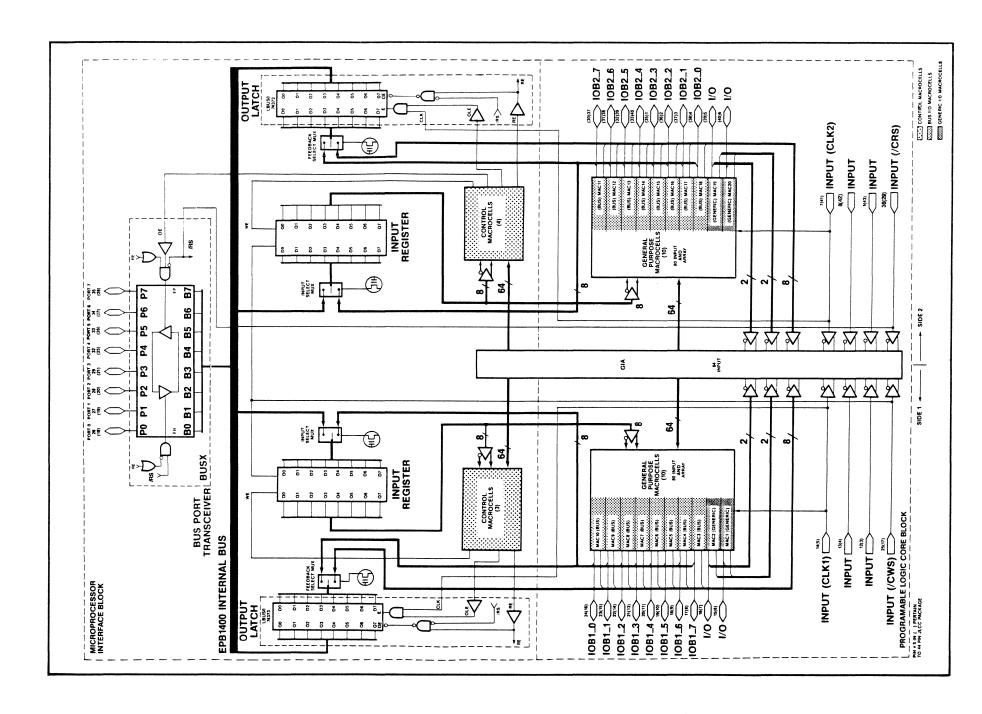

The following pages provide detailed descriptions of the Bus I/O primitives, which are available for use with the EPB1400 ("BUSTER").

The following rules apply to Bus I/O primitives:

- 1. Each BUSTER (EPB1400) part may use 0 or 1 BUSX primitive; 0, 1, or 2 LBUSO primitives; and 0, 1, or 2 primitives selected from the following group: LBUSI, LINP8, RBUSI and RINP8.

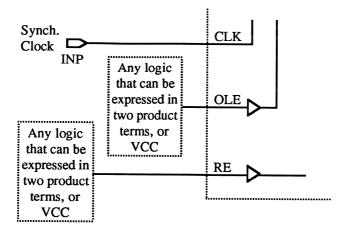

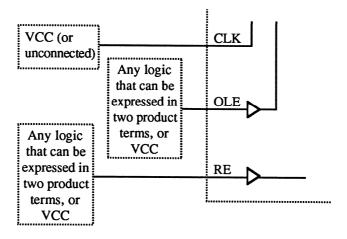

- 2. The Clock (Clk) input to the LBUSO primitive is optional. If it is connected, it must be connected directly to a pin or VCC (latch enabled). When the Clk input is connected, the value of an unconnected Output Latch Enable (Ole) input will default to VCC. If the Clk is left unconnected, logic must be connected to the Ole, which will have full control of the latch. If either input is left unconnected, you must retain the comma that delimits the field.

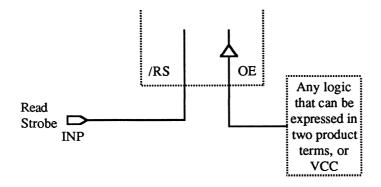

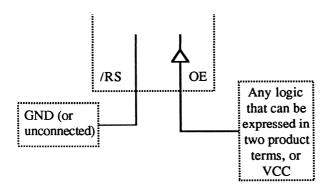

- 3. The Read Strobe (Rs) input to the BUSX primitive is optional. This signal is predefined as an active low input, therefore, it is not necessary to invert the signal to implement active low logic. If the Rs is connected, it must be connected directly to the dedicated pin (/CRS) or to GND. When the Rs input is connected, the value of an unconnected Output Enable (Oe) input will default to VCC, allowing the bus port to drive the internal bus. If the Rs is left unconnected, logic must be connected to the Oe, which will have full control of the bus transceiver. If either input is left unconnected, you must retain the comma that delimits the field.

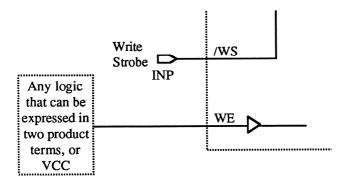

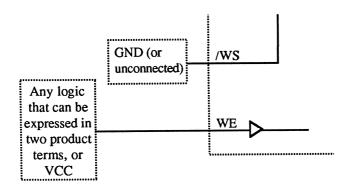

- 4. The Write Strobe (Ws) input to the LBUSI, LINP8, RBUSI, and RINP8 primitives is optional. This signal is predefined as an active low input, therefore, it is not necessary to invert the signal to implement active low logic. If the Ws is connected, it must be connected directly to the dedicated pin (/CWS) or GND. When the Ws input is connected, the value of an unconnected Write Enable (We) input will default to VCC (latch/register enabled). If the Ws is left unconnected, logic must be connected to the We, which will have full control of the latch/register. If either input is left unconnected, you must retain the comma that delimits the field.

5. The logic feeding the Write Enable (We), Read Enable (Re), Output Latch Enable (Ole), and Output Enable (Oe) inputs may contain up to two product terms.

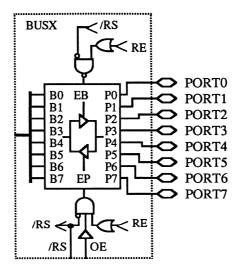

## BUSX

Name: BUSX (Bus Transceiver)

ADF Syntax: Out0, Out1, Out2, Out3, Out4, Out5, Out6,

Out7 = BUSX(Ibus, Rs, Oe)

Description: Outputs:

Out(0-7) = EPLD port pin outputs

(PORT0-7)

Inputs:

Ibus = (internal bus) output from logic array

Rs = read strobe input (active low)

Oe = 3-state buffer output enable input

EPLDs: EPB1400 (BUSTER)

Notes:

1. The OR gates in this primitive are fed by the

Read Enable (Re) output of up to two LBUSO

primitives.

- 2. The Read Strobe (Rs) input to the BUSX primitive is optional. This signal is predefined as an active low input, therefore, it is not necessary to invert the signal to implement active low logic. If the Rs is connected, it must be connected directly to the dedicated pin (/CRS) or to GND. When the Rs input is connected, the value of an unconnected Output Enable (Oe) input will default to VCC, allowing the bus port to drive the internal bus. If the Rs is left unconnected, logic must be connected to the Oe, which will have full control of the bus transceiver. If either input is left unconnected, you must retain the comma that delimits the field.

- 3. The Read Strobe (Rs) output of this primitive is the Rs used by an LBUSO primitive.

- 4. The Read Enable (Re) input of this primitive is the supplied by an LBUSO primitive.

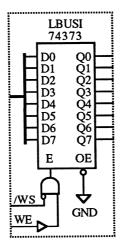

#### **LBUSI**

Name: LBUSI (Latched Bus Input to Logic)

ADF Syntax: Out0, Out1, Out2, Out3, Out4, Out5, Out6,

Out7 = LBUSI(Ibus, Ws, We)

Description: Outputs:

Out(0-7) = output to logic array (Q0-Q7)

Inputs:

Ibus = internal bus

Ws = write strobe input (active low)

We = write enable input

EPLDs: EPB1400 (BUSTER)

Notes:

1. The Write Strobe (Ws) input to this primitive is optional. This signal is predefined as an active low input, therefore, it is not necessary to invert the signal to implement active low logic. If the Ws is connected, it must be connected directly to the dedicated pin (/CWS) or GND. When the Ws input is connected, the value of an unconnected Write Enable (We) input will default to VCC (latch

enabled). If the Ws is left unconnected, logic must be connected to the We, which will have full control of the latch. If either input is left unconnected, you must retain the comma that delimits the field.

2. The logic feeding the Write Enable (We) input may contain up to 2 product terms.

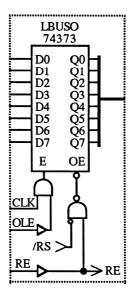

#### **LBUSO**

Name: LBUSO (Latched Bus Output from Logic)

ADF Syntax: Ibus = LBUSO(In0, In1, In2, In3, In4,

In5, In6, In7, Clk, Ole, Re)

Description: Outputs:

Ibus = Internal bus

Inputs:

In(0-7) = EPLD pin inputs or macrocell

feedbacks (D0-D7)

Clk = clock input

Ole = output latch enable

Re = read enable

EPLDs: EPB1400 (BUSTER)

Notes: 1. The Clock (Clk) input to the LBUSO primitive is

optional. If it is connected, it must be connected directly to a pin or VCC (latch enabled). When the

Clk input is connected, the value of an unconnected Output Latch Enable (Ole) input will default to VCC. If the Clk is left unconnected, logic must be connected to the Ole, which will have full control of the latch. If either input is left unconnected, you must retain the comma that delimits the field.

- 2. The logic feeding the Output Latch Enable (Ole) and Read Enable (Re) inputs may contain up to 2 product terms.

- 3. The Read Strobe (Rs) input to this primitive is supplied by the BUSX primitive.

- 4. The Read Enable (Re) output of this primitive is the Re used by a BUSX primitive.

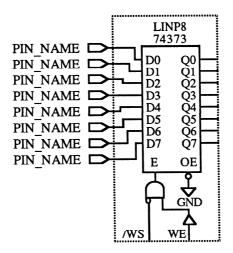

# LINP8

Name:

LINP8 (8-Bit Latched Pin Input to Logic)

ADF Syntax:

Out1, Out2, Out3, Out4, Out5, Out6, Out7 = LINP8(In0, In1, In2, In3, In4, In5, In6, In7, Ws, We)

Description:

Outputs:

Out(0-7) = outputs to logic array (Q0-Q7)

Inputs:

In(0-7) = EPLD pin inputs

Ws = write strobe input (active low)

We = write enable input

EPLDs:

EPB1400 (BUSTER)

Notes:

1. The Write Strobe (Ws) input to this primitive is optional. This signal is predefined as an active low input, therefore, it is not necessary to invert the signal to implement active low logic. If the Ws is connected, it must be connected directly to the dedicated pin (/CWS) or GND. When the Ws input

is connected, the value of an unconnected Write Enable (We) input will default to VCC (latch enabled). If the Ws is left unconnected, logic must be connected to the We, which will have full control of the latch. If either input is left unconnected, you must retain the comma that delimits the field.

2. The logic feeding the Write Enable (We) input may contain up to 2 product terms.

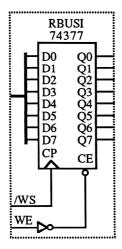

#### **RBUSI**

Name:

**RBUSI** (Registered Bus Input to Logic)

ADF Syntax:

Out0, Out1, Out2, Out3, Out4, Out5, Out6,

Out7 = RBUSI(Ibus, Ws, We)

Description:

Outputs:

Out(0-7) = output to logic array (Q0-Q7)

Inputs:

Ibus = internal bus

Ws = write strobe input (active low)

We = write enable input

EPLDs:

EPB1400 ("BUSTER")

Notes:

1. The Write Strobe (Ws) input to this primitive is optional. This signal is predefined as an active low input, therefore, it is not necessary to invert the signal to implement active low logic. If the Ws is connected, it must be connected directly to the dedicated pin (/CWS) or GND. When the Ws input is connected, the value of an unconnected Write Enable (We) input will default to VCC (register

enabled). If the Ws is left unconnected, logic must be connected to the We, which will have full control of the register. If either input is left unconnected, you must retain the comma that delimits the field.

2. The logic feeding the Write Enable (We) input may contain up to 2 product terms.

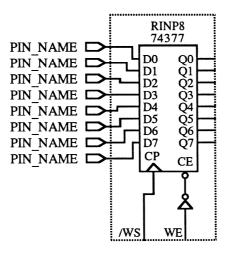

#### RINP8

Name:

RINP8 (8-Bit Registered Pin Input to Logic)

ADF Syntax:

Out0, Out1, Out2, Out3, Out4, Out5, Out6, Out7 = RINP8(In0, In1, In2, In3, In4, In5, In6, In7, Ws, We)

Description:

Outputs:

Out(0-7) = outputs to logic array (Q0-Q7)

Inputs:

In(0-7) = EPLD pin inputs

Ws = write strobe input (active low)

We = write enable input

EPLDs:

EPB1400 (BUSTER)

Notes:

1. The Write Strobe (Ws) input to this primitive is optional. This signal is predefined as an active low input, therefore, it is not necessary to invert the signal to implement active low logic. If the Ws is connected, it must be connected directly to the dedicated pin (/CWS) or GND. When the Ws input

is connected, the value of an unconnected Write Enable (We) input will default to VCC (register enabled). If the Ws is left unconnected, logic must be connected to the We, which will have full control of the register. If either input is left unconnected, you must retain the comma that delimits the field.

2. The logic feeding the Write Enable (We) input may contain up to 2 product terms.

#### SECTION 2

# Altera Design File Format

This section describes the functions and syntax of the Altera Design File (ADF). It includes a detailed description of the syntax of each section of the Altera Design File and a sample ADF.

## **Functions**

The Altera Design File has several functions:

- It is the common design entry format for A+PLUS software.

- It is the output of the State Machine and FutureNet Pinlist Converter programs.

- It is the output of the LogiCaps schematic capture software.

- It is the input to the Altera Design Processor.

- It is the entry format of the Boolean Equation and Netlist design entry methods.

## **Syntax**

This description of the Altera Design File follows the Backus-Naur Form (BNF) conventions. The ADF syntax for each individual section is described in the paragraphs below. A full BNF description of the ADF syntax is also given in Figure 2-1. (See *Appendix C* for a description of BNF rules.)

The ADF has the following syntax:

<adf netlist> ::= [<header>] <declarations> <network> [<equations>] 'END\$'

### **Keywords**

All ADF keywords—OPTIONS:, PART:, INPUTS:, OUTPUTS:, NETWORK:, and EQUATIONS:—must be the first word in the line in which they appear. (Do not enter comments, tabs, or blank spaces before keywords.)

### White Space and Comments

White space is defined as blank spaces, tabs, carriage returns, and line feeds. White space may be inserted between syntax elements to enhance readability, except in the following cases:

- Within any name.

- Between prefix> and <expression> or <expression> and <postfix> in a Boolean expression. (Refer to Equations Section.)

- Before keywords, as described in the preceding section

Comments must be enclosed by percent symbols (%). They may contain any printable character except the delimiter %. They may be inserted wherever white space is allowed, *except* within the Header Section of a file.

The comment string syntax is defined as follows:

**Header Section**

< tab > ::= < hex 09 >

<space> ::= <hex 20>

<EOL> ::= <hex 0D> <hex 0A>

The optional Header Section of the Altera Design File serves to identify a design entered by the user. This section has several important uses and restrictions:

- It is included in the header of the Utilization Report, the Logic Equation File, and the JEDEC File.

- Any printable character except the asterisk (\*) is allowed.

- If it is present, it must be the first section in the ADF.

- It is terminated by either the OPTIONS: or PART: keywords, which A+PLUS recognizes as the start of the Declarations Section.

Information in the Header Section must appear in the following order, with one item on each line. The maximum character countfor each field is indicated in parentheses.

- 1. Designer (48) 2. Company (60) 3. Date (24) 4. Number (24) 5. Revision (24)

- 6. EPLD (10)

- 7. Comment (512)

<EOL> ::= <hex 0D> <hex 0A>

<space> ::= <hex 20>

8. Any other information (may be more than one line)

The Header Section has the following syntax:

#### **Declarations Section**

The Declarations Section consists of four (sub)sections:

- Options Section—contains the Turbo-Bit and Security Bit options, which allow you to set the Turbo-Bit and Security Bit to ON or OFF. (If you do not specify ON or OFF, the Turbo-Bit defaults to ON and the Security Bit defaults to OFF.) (The BUSTER (EPB1400) and EP310 parts do not support the Turbo-Bit option. LogicMap will ignore any Turbo-Bit information entered for these EPLDs.)

- Part Section—contains a target part number, AUTO (for automatic part selection), or MACRO if you are creating a MacroFunction with ADLIB (available with LogiCaps).

- Inputs Section—contains input signal designations, including optional pin assignments.

- Outputs Section—contains output signal designations, including optional pin assignments.

The Declarations Section has the following syntax:

```

<declarations> ::= [<options>] <part> <inputs> <outputs>

where

<options> ::= 'OPTIONS:' <opt spec> {[ ',' ] <opt spec>} <EOL>

<part> ::= 'PART:' <part name> <EOL>

<inputs> ::= 'INPUTS:' <i/o list> <EOL>

<outputs> ::= 'OUTPUTS:' <i/o list> <EOL>

where

<opt spec> ::= <opt name> [ '=' <opt value>]

<part name> ::= 'EP310' | 'EP310D' | 'EP320' | 'EP320D' | 'EP600D' | 'EP600D' | 'EP600J' | 'EP610' | 'EP610D' | 'EP910J' | 'EP910D' | 'EP1210' | 'EP1210D' | 'EP1210J' | 'EP1210J' | 'EP1210J' | 'EP1210J' | 'EP1210J' | 'EP1210J' | 'EP1800J' | 'EP1800J' | 'EP1800G' | 'AUTO' | 'MACRO'

<i/option="mailto:single-specific list | '', '<opt name> { ',' <i/op name> }

```

#### where

- 1. To use the automatic part selection feature, simply enter AUTO instead of a specific part name after the PART: keyword. The ADP will automatically choose the part most likely to fit your design. (Automatic part selection will not be successful if you specify pin assignments, or if there are too many inputs, outputs, or macrocells in the design.)

- 2. If you use an asterisk (\*) in an input or output pin name, it will be converted into a tilde (~) in the JEDEC file generated by the ADP. You must ensure that this conversion will not create duplicate pin names (for example, if you use both \* and ~ when naming pins).

- 3. The ADP creates internal node names that contain periods (.). User-assigned pin names that contain periods may occasionally conflict with these node names and cause unpredictable results.

- 4. The Functional Simulator ignores all user-defined pin names that contain periods (periods are allowed only for referencing internal nodes of I/O primitives).

#### **Network Section**

The Network Section specifies the input, output, and I/O architecture to be programmed. Primitive statements control the pin connections to internal logic and I/O macrocell configurations.

```

The Network Section has the following syntax:

<network> ::= 'NETWORK:' <network list>

where

<network list> ::= <primitive equation> | <MacroFunction statement>

where

<primitive equation> ::= <parameters> '=' <primitive> '(' <parameters> ')'

<MacroFunction statement> ::= <MacroFunction> '(' <parameters> ')'

where

<parameters> ::= <pin name> | <name> {',' <name>}

cprimitive> ::= <any Altera Primitive name>

(e.g., CONF, INP, NORF)

<MacroFunction> ::= <any user-defined or Altera MacroFunction name>

(e.g., UNICNT, 74393)

where

<pin name> ::= <pin char>:1:8

<name> ::= <name char>:1:8

where

<pin char> ::= <any printable ASCII character except comma, %, @, =, (, )>

<name char> ::= <digit> | <alphabet letter>

where

<digit> ::= '0' | '1' | ... | '9'

<alphabet letter> ::= 'A' | 'B' | ... | 'Z' | 'a' | 'b' | ... | 'z'

```

Refer to *Altera Primitive Library* for primitive names and syntax. MacroFunction names and syntax are given in the optional *LogiCaps* and *TTL MacroFunctions* packages.

#### **Equations Section**

The optional Equations Section supports the direct entry of logical equations. It consists of the keyword EQUATIONS:, followed by zero or more logical equations. Each equation has exactly one node name on the left, an equals sign (=), a Boolean expression, a semicolon (;), and an End-of-Line (EOL) sequence.

```

The Equations Section has the following syntax:

<equations> ::= 'EQUATIONS:' {<logic equation>}

where

<logic equation> ::= <LHS> '=' <expression> ';' <EOL>

where

<LHS> ::= refix><name> | <name> | <name><postfix>

(no white space is allowed between <prefix><name> and

<name><postfix>)

<expression> ::= <name> | <prefix><expression> | <expression><postfix> |

<expression> <infix> <expression> | '(' <expression> ')'

(no white space is allowed between <prefix><expression> and

<expression><postfix>)

where

'' | '!'

<infix> ::= '+' | '*' | '#' | '&'

<postfix> ::= ""

<name> ::= <name char>:1:8

where

<name char> ::= <digit> <alphabet letters>

```

#### where

$$\begin{array}{l} <\!\! digit> ::= '0' \mid '1' \mid ... \mid '9' \\ <\!\! alphabet \ letters> ::= 'A' \mid 'B' \mid ... \mid 'Z' \mid 'a' \mid 'b' \mid ... \mid 'z' \end{array}$$

#### **End Statement**

This statement terminates the ADF. It has the following syntax:

```

<adf netlist> ::= [<header>] <declarations> <network> [<equations>] 'END$'

<header> ::= <header char>:0:48 <EOL>

<header char>:0:60 <EOL>

<header char>:0:24 <EOL>

<header char>:0:24 <EOL>

<header char>:0:24 <EOL>

<header char>:0:10 <EOL>

<header char>:0:512 < EOL>

{{<header char>} <EOL> {{<header char>} <EOL>}

<header char> ::= <tab> | <space> | <hex 21> | ... | <hex 29> | <hex 2B> |

<hex 2C> | ... | <hex 7E>

(i.e., any printable ASCII character except an asterisk (*))

<tab> ::= <hex 09>

<EOL> ::= <hex 0D> <hex 0A>

<space> ::= <hex 20>

<declarations> ::= [<options>] <part> <inputs> <outputs>

<options> ::= 'OPTIONS:' <opt spec> {[ ',' ] <opt spec>} <EOL>

<part> ::= 'PART:' <part name> <EOL>

<inputs> ::= 'INPUTS:' <i/o list> <EOL>

<outputs> ::= 'OUTPUTS:' <i/o list> <EOL>

<opt spec> ::= <opt name> [ '=' <opt value>]

<opt name> ::= 'TURBO' | 'SECURITY'

<opt value> ::= 'ON' | 'OFF'

<part name> ::= 'EP310' | 'EP310D' | 'EP320' | 'EP320D' | 'EP600D' | 'EP600D'

| 'EP600J' | 'EP610' | 'EP610D' | 'EP610J' | 'EP900' | 'EP900D' |

'EP900J' | 'EP910' | 'EP910D' | 'EP910J' | 'EP1210' | 'EP1210D' |

'EP1210J' | 'EPB1400' | 'EPB1400D' | 'EPB1400J' | 'EP1800' |

'EP1800J' | 'EP1800G' | 'AUTO' | 'MACRO'

<i/o list> ::= <i/o name> {',' <i/o name>}

<i/o name> ::= <pin name> [ '@' <pin number>]

<pin name> ::= <pin char>:1:8

<pin char> ::= <any printable ASCII character except comma, %, @, =, (, )>

<pin number> ::= [<letter prefix>] <digit> [<digit>]

<letter prefix> ::= 'A' | 'B' | ... | 'H' | 'J' | 'K' | 'L'

(letter prefix allowed only in EP1800G pin numbers)

<digit> ::= '0' | '1' | ... | '9'

```

Figure 2-1. BNF Syntax for Altera Design File (Part 1 of 2)

```

<network> ::= 'NETWORK:' <network list>

<network list> ::= <primitive equation> | <MacroFunction statement>

<primitive equation> ::= <parameters> '=' <primitive> '(' <parameters> ')'

<MacroFunction statement> ::= <MacroFunction> '(' <parameters> ')'

<parameters> ::= <pin name> | <name> {',' <name>}

<name> ::= <name char>:1:8

<name char> ::= <digit> | <alphabet letter>

cprimitive> ::= <any Altera Primitive name>

(e.g., CONF, INP, NORF)

<MacroFunction> ::= <any Altera or user-defined MacroFunction name>

(e.g., UNICNT, 74393)

<equations> ::= 'EQUATIONS:' {<logic equation>}

<logic equation> ::= <LHS> '=' <expression> ';' <EOL>

<LHS> ::= <prefix><name> | <name> | <name><postfix>

(no white space is allowed between <prefix><name> and

<name><postfix>)

<expression> ::= <name> | <prefix><expression> | <expression><postfix> |

<expression> <infix> <expression> | '(' <expression> ')'

(no white space is allowed between cprefix><expression> and

<expression><postfix>)

<prefix> ::= '/' | '!'

<infix> ::= '+' | '*' | '#' | '&'

<postfix> ::= "

'END$'

```

Figure 2-1. BNF Syntax for Altera Design File (Part 2 of 2)

## **Netlist Files**

Using a standard text editor, you can type a netlist corresponding to your design into the ADF format. You may also adapt the netlist output of another design interface to the ADF format. (For guidelines on ADF entry, refer also to *Boolean Equation Entry* in the **A+PLUS User Guide**.)

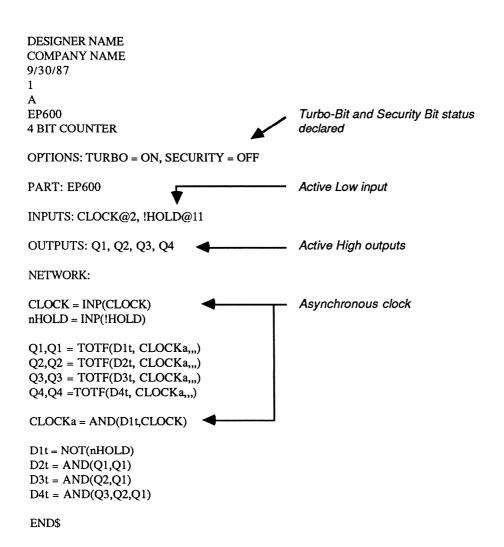

Figure 2-2 shows a sample ADF. Using only netlist format, this ADF describes the same 4-bit counter design shown in Figure BE-6 in *Boolean Equation Entry*.

Figure 2-2. Sample ADF

#### SECTION 3

# A+PLUS and ADP Reference

#### This section contains:

- A detailed description of the functions available on the APLUS Menu

- A detailed description of the functions available on the ADP Menu

- A summary of the automatic functions of the Altera Design Processor (ADP)

- Instructions for running or invoking A+PLUS programs from the DOS command line (i.e., stand-alone mode)

For detailed information on using A+PLUS, see the individual design entry method sections of the *A+PLUS User Guide*.

## **APLUS Menu Functions**

The APLUS Menu provides access to the following:

- Help

- Text editor of your choice

- Altera Design Processor (ADP)

- LogicMap II

- Functional Simulator (an optional package)

- Current directory

- Any DOS command

To invoke the APLUS Menu, type at the DOS prompt:

#### APLUS <Enter>

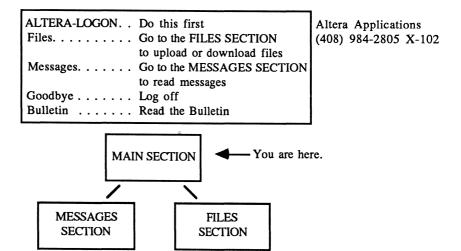

The APLUS Menu is displayed, as shown in Figure 3-1.

Figure 3-1. APLUS Menu

The current (default) menu selection, <F4> (ADP), is highlighted. The numbers displayed on the left of the menu selections show the function keys used to execute each function. You may also select functions with the <\$\ddagger\$> and <\$\famound{\text{res}}\$ and <Enter>.

#### The APLUS Menu functions are:

- <F1> Help Displays helpful information on APLUS Menu functions. After pressing <F1>, you may use the function or <↓> and <↑> keys to display a help message for each menu function. Press <Enter> to quit the Help function.

- <F2> Exit Terminates A+PLUS and returns you to DOS. (Use the DOS Command (<F8>) function to execute DOS commands during the current A+PLUS session.)

- <F3> <LogiCaps> Invokes the text editor or schematic capture program of your choice. LogiCaps is the default, but you can override the default by entering another editor (e.g., WordStar) during installation.

- <F4> ADP Invokes the menu for the Altera Design Processor (ADP). The functions controlled by the ADP Menu allow you to process your design file into a JEDEC file used for programming an Altera EPLD. (See ADP Menu Functions below.)

- <F5> LogicMap II Invokes the LogicMap II program, which allows you to program an Altera EPLD with A+PLUS hardware. If you attempt to use this function when the Logic Programmer card is not installed, the following message is displayed:

#### Programmer self test failed

Device must NOT be in socket for this test to pass!

#### Enter:

C to continue without programming card

T to run diagnostics again

Q to return to operating system

- (See the **LogicMap II** manual for detailed information on device programming.)

- <F6> Func Simulator Invokes Altera's Functional Simulator (an optional package). Refer to the Functional Simulator section of the A+PLUS User Guide.

- <F7> Directory Allows you to enter a search pattern. You may enter a drive or path name with asterisk (\* for any sequence) and question mark (? for any single character) characters for pattern matching. A+PLUS then displays a list of DOS matching the pattern.

- <F8> DOS command Temporarily returns you to DOS so that you can enter a DOS command. After entering the DOS command, type EXIT to return to APLUS. (Note: Do not re-invoke A+PLUS while in this temporary DOS environment—a duplicate copy of A+PLUS will be read into memory.)

### **ADP Menu Functions**

Several important Altera Design Processor features are controlled by the functions associated with the ADP Menu. This menu allows you to specify the conditions used for compiling your design file.

#### The ADP Menu allows you to:

- Request on-line help

- Return to the APLUS Menu

- Specify input file format

- Specify input file name(s)

- Request logic minimization

- Control logic inversion

- Request LEF Analysis

- Execute the ADP

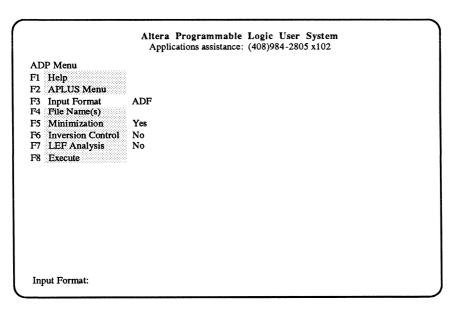

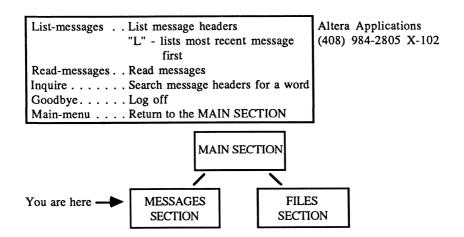

To invoke the ADP Menu, press <F4> while in the APLUS Menu. The screen clears and the ADP Menu is displayed, as shown in Figure 3-2.

The numbers displayed on the left of the menu selections show the function keys used to execute each function. The current (default) menu selection, <F3> (Input Format), is highlighted. This function is the first in the default sequence for entering processing parameters, but you may move around the menu and enter and change processing options in any order. (Use the Function keys <F1> through <F8> or the <1>, <1>, and <Enter> keys.) You can accept the default processing settings, which are shown on the right of the function names, by simply pressing <Enter>.

As each parameter is entered, it appears on the bottom line of the screen and may be edited with the  $\leftrightarrow$  and  $\leftarrow$  cursor keys, as well as the <Del>, <Backspace>, <Home>, and <End> keys.

Figure 3-2. ADP Menu

The ADP Menu functions are:

- <F1> Help Displays helpful information on ADP Menu functions. After pressing <F1>, you may use the function or <\$\frac{1}{2}\$ and <\$\frac{1}{2}\$ keys to display a help message for each menu function. Press <Enter> to quit the Help function.

- <F2> APLUS Menu Terminates the current ADP session and returns you to the APLUS Menu.

<F3> Input Format Prompts you for the format of your input file:

A or <Enter> - for an Altera Design File with the extension

.ADF (the default)

for a component list with the extension

.CMP, as output by P-CAD's PC-CAPS

for a pinlist with the extension .PIN, as

output by FutureNet's DASH Schematic

Design Editor

for a State Machine File with the extension

.SMF

<F4> File Name(s) Prompts you for the name(s) of file(s) containing your design. You need not enter the filename extension.

If you type?, you are prompted with File/Directory search pattern:. If you press <Enter>, a list of files in the current directory with the extension specified in Input Format <F3> is displayed. If you enter a path or drive name, a list of the files in the specified drive and/or directory is displayed. The most recently updated file is then provided as a default.

You may enter up to 9 input filenames, separated by blanks or commas. If any filename has a different extension from the one entered at the <F3> prompt, you must type both the filename and extension. (All files will be automatically converted into ADFs and processed into a single JEDEC file.)

<F5> Minimization Allows you to request a reduction of the Boolean logic of the design. If you enter Y (Yes [the default]), Boolean minimization is performed on the design. If you enter N (No), minimization is not performed and the ADP Menu selection automatically moves to the LEF Analysis (<F7>) prompt.

<F6> Inversion Control Allows you to request control over inversion of individual Boolean equations during the minimization process. If you enter Y (Yes), you are asked on an equation-by-equation basis whether you wish to perform a De Morgan's inversion. This feature is useful mainly for unusual EP310 and EP1210 designs. For other EPLDs, you should enter N (No [the default]). The ADP then quickly inverts each equation to determine whether the inverted form reduces further than the non-inverted form. (In either case, the actual output of the pin remains the same, and the equation is retained in the form that contains the fewest product terms. If both forms contain the same number of product terms, the non-inverted form is retained.)

Every time the ADP asks whether you wish to perform an inversion on a particular equation, information on the equation's current status is displayed, including the product-term count after the first pass through the reduction algorithm and the symbol on the left-hand side of the equation. If this symbol is complemented, the equation has already been inverted by the software, and an inversion will cause the left-hand side of the equation to be uncomplemented.

<F7> LEF Analysis Allows you to request the ADP to analyze the intermediate Logic Equation File (LEF). If you enter Y (Yes), this module converts the intermediate LEF output by the Expander (or Minimizer) into a format similar to that of the ADF. This file appears in the current directory with the extension .LEF, and allows you to view the design after it has been translated, expanded, and, if requested at the <F5> prompt, minimized.

The LEF records the name of the input ADF and the ADP options you selected for processing to the header section of the file. It also documents any primitives that were promoted to different primitives, and, if necessary, inserts default values for the Turbo-Bit and Security Bit. The .LEF file enables you to check the pin assignments and the product term count, and to determine whether design modifications are needed to assist in the fitting process. After examining the LEF, you may wish to edit your input file and resubmit it to the ADP. (For an example of ADF-to-LEF translation, see *Appendix B*.)

For large designs, a non-minimized LEF may provide convenient breakpoints for partitioning. (More opportunities for partitioning can be found in the non-minimized representation of a design.) Note, however that there may not be enough memory to complete design processing (i.e., you will probably obtain an LEF but not a JEDEC file).

If you enter N (No [the default]) at the LEF Analysis prompt, the ADP indicates that you have answered the prompts for <F3> through <F7>, by asking:

Do you wish to run under the above conditions [Y/N]?

Enter Y or press <F8> (Execute) to execute the ADP. If you enter N, the ADP Menu returns to the Input Format function (<F3>), allowing you to change any of the previously entered parameters.

<F8> Execute Immediately processes the design according to the current menu options. (You are prompted for a filename if you have not entered one previously.)

This function also allows you to repeat processing during design iterations. If you need to edit a design, use the Editor (<F3>) function on the A+PLUS Menu to edit your input file. When you exit from your editor (e.g., LogiCaps) you are automatically returned to the APLUS Menu. Then, press <F4> to return to the ADP Menu and press <F8> to repeat design processing. The previous menu settings, including the name of the most recently processed file, will remain in effect until they are explicitly changed.

When the ADP has finished processing the design, you are asked:

Would you like to implement another design [Y/N]?

If you enter Y, a new loop through the ADP Menu is initiated. If you enter N, you are returned to the APLUS Menu.

## **Automatic ADP Functions**

Many functions of the Altera Design Processor are built into the A+PLUS software and are not user-controllable. The ADP *automatically* performs these tasks during normal design processing (i.e., they cannot be altered with the APLUS or ADP Menu functions). When used with the menu options described above, the ADP is a powerful tool for compiling and fitting an EPLD design.

#### The ADP's automatic functions are:

- Displays information, error, and warning messages, which are prefixed with \*\*\*INFO-, \*\*\*ERR-, and \*\*\*WARN-, respectively. Many A+PLUS information messages simply indicate that a particular ADP module has completed execution without error. (For detailed information, see A+PLUS Messages.)

- Logs all information, error, and warning messages to a file called ADP.LOG in the current directory. This file is overwritten each time the ADP is invoked.

- Expands Boolean equations in the ADF into sum-of-products form, checks for evidence of combinatorial feedback, and removes redundant factors from product terms.

- Checks the ADF for MacroFunction statements, which are expanded and replaced with primitive statements. The ADP then converts the ADF into a file with the extension .SDF, and continues design processing. (No action is taken if MacroFunction statements are not present.)

- Translates the .ADF or .SDF (from the previous step) into internal logic equations.

- Selects an appropriate EPLD for the design if automatic part selection is requested in the input design file.

- Generates a Utilization Report (.RPT file) that documents macrocell and pin assignments, pin names, and buried registers, as well as any unused resources in the target EPLD.

- Generates a JEDEC file with the extension .JED for programming an Altera EPLD.

## Running A+PLUS Programs from DOS

A+PLUS software allows you to invoke and/or run the Altera Design Processor, Functional Simulator, FutureNet Pin List Converter (FCV), LogiCaps schematic capture package, LogicMap II program, and State Machine Converter (SMV) directly from DOS (i.e., in stand-alone mode). The following pages describe how to invoke and/or run these programs from the DOS command line.

Stand-alone execution of the ADP, SMV, or FCV increases the available memory for larger designs by approximately 70 Kbytes.

Stand-alone execution of the SMV and FCV allows you to create a design in several stages. For example, you may wish to combine design data from input files with different formats. By using DOS commands, you can run these converters without running the ADP, and examine the resulting ADFs before further processing is initiated. After State Machine and/or FutureNet Pin List files have been converted into ADFs, they may be combined for processing by the ADP.

- 1. In the following descriptions, command line options are shown in square brackets ([]); required items are shown without brackets.

- 2. On-screen messages are the same for Command Line mode and Menu mode.

## **Altera Design Processor**

To run the ADP from the DOS command line, type:

ADP [-mdl] <filename> <Enter>

where the command line options have the following meaning:

- -m perform minimization

- -d manually control De Morgan's inversion

- -I run LEF Analyzer

You may use any combination of these options, e.g., -ml. The filename extension .ADF is assumed.

#### **Functional Simulator**

To run the Functional Simulator in *batch mode* from the DOS command line, type:

FSIM <filename> <Enter>

Do not type the JED filename extension.

To run the Functional Simulator in *interactive mode* from the DOS command line, type:

FSIM <Enter>

#### FutureNet Pin List Converter

To run the FutureNet Pin List Converter from the DOS command line, type:

FCV <filename> <Enter>

The filename extension .PIN is assumed.

#### LogiCaps

To invoke LogiCaps from the DOS command line, type:

LOGICAPS [filename] [@macroname] [options] <Enter>

where the command line options have the following meaning:

filename (optional) The name of a design file to be automatically

loaded.

macroname (optional) The name of a macro recorded and written to

a file with the extension  $\boldsymbol{.}\mathbf{MAC}.$  It is used instead of

INIT.MAC.

options Additional configuration specifications that you may enter when invoking LogiCaps. The available options

are:

-1 Use COM1 for the mouse (the default).

-2 Use COM2 for the mouse.

-l <symbol library> Selects a different symbol library. The default is ALTERA.SYM.

-ml Increase the memory for LINE objects. This option allows you to reallocate memory to increase the memory capacity for lines.

-ms Increase the memory for SYMBOL objects. This option allows you to reallocate memory to increase the memory capacity for symbols.

-mt Increase the memory for TEXT objects. This option allows you to reallocate memory to increase the memory capacity for text entries.

-x Set new file configuration data. This option lets you ignore configuration specifications in LOGICAPS.CFG and prompts you for new configuration information.

For a screen display of this information, type at the DOS prompt:

LOGICAPS ? <Enter>

## LogicMap II

To invoke LogicMap II from the DOS command line, type:

LOGICMAP <Enter>

#### State Machine Converter

To run the State Machine Converter from the DOS command line, type:

SMV <filename> <Enter>

The filename extension .SMF is assumed.

#### **SECTION 4**

## Utilization Report

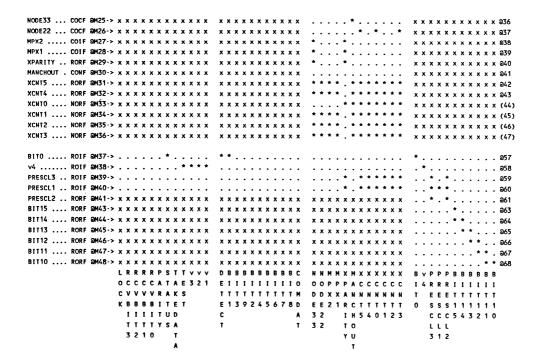

This section describes the Utilization Report and provides several sample .RPT files.

The Utilization Report is generated by the Fitter module of the Altera Design Processor. This report documents how an EPLD's resources (i.e., pin and macrocell assignments, input and output pin names, and buried registers) were used by a design, as well as any unused resources. The Utilization Report is automatically stored and listed in the directory containing the input design file as filename.RPT.

If you have specified all pin assignments and the design fits, you need not refer to the Utilization Report. However, if you did not specify all pin assignments, you should to refer to this report to determine which pin assignments were selected by the Fitter.

Utilization Report 4-1

When fitting a design, the Fitter module first tries to fit any pin assignments requested in the design file. If the Fitter is unable to accommodate a pin assignment, it displays a message asking whether the request can be ignored. If you enter Y (Yes), all pin requests are ignored and the Fitter continues; if you enter N (No), the Fitter terminates.

For additional information, refer to *Appendix A*, which explains macrocell groups for each EPLD. This information will assist you in choosing pin assignments that will enable the Fitter to find a satisfactory fit for your design.

### **Header Information**

The first line of a Utilization Report contains a statement indicating whether a design has been implemented successfully.

This line is followed by the ADF header information, including the input filename(s) and ADP options requested for design processing, and a representation of the target EPLD that shows both used and unused pins.

GND indicates unused input pins and unused macrocell group pins (except for the actual GND pins). Pins marked GND must be connected to ground; they should never be left floating.